## **MtronPTI HPO Series For Harsh Environment Applications**

**Electrical Specifications:**

| Parameter                                                  | Symbol            | Min.                          | Тур.         | Max.                | Units  | Conditions                                                                                                                      |

|------------------------------------------------------------|-------------------|-------------------------------|--------------|---------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| Frequency of Operation                                     | Fo                | 25.000                        |              | 150.000             | MHz    |                                                                                                                                 |

|                                                            |                   |                               | Frequency    | y Stabilities       |        |                                                                                                                                 |

| Frequency Stability Over the Temperature Range             | ΔF/F              | -5                            |              | +5                  | ppm    | Over -55°C to +125°C<br>(F <sub>Max</sub> - F <sub>Min</sub> )/2                                                                |

| Total Frequency Stability Over 20-years (ref. Model Table) |                   | -25<br>-50                    |              | +25                 | ppm    | Includes tolerance at +25°C, variation in supply voltage, deviation over operating temperature range and 20 years aging @ +25°C |

|                                                            |                   | 50                            | <u> </u>     | tput                |        | range and 20 years aging 0 +25 0                                                                                                |

| Output Type                                                |                   | HC                            | MOS/TTL Comp |                     |        |                                                                                                                                 |

| Output Load                                                |                   | TIC                           | 15           | atible              | pF/TTL |                                                                                                                                 |

| Symmetry (duty cycle)                                      | $T_{DC}$          | 45                            | 15           | 55                  | %      | ½ V <sub>DD</sub>                                                                                                               |

| Logic "1" Level                                            | V <sub>OH</sub>   | 90% V <sub>DD</sub>           |              |                     | V      |                                                                                                                                 |

| Logic "0" Level                                            | V <sub>OL</sub>   | DD                            |              | 10% V <sub>DD</sub> | V      | HCMOS load                                                                                                                      |

| Rise/Fall Time                                             | $T_R/T_F$         |                               | 1.8          | 3                   | nS     | From 10% to 90% V <sub>DD</sub>                                                                                                 |

| Random Jitter                                              |                   |                               |              | 4                   | pS RMS |                                                                                                                                 |

| Phase Jitter                                               | фл                |                               |              | 1                   | pS RMS | Integrated 12kHz to 20MHz                                                                                                       |

| Period Jitter                                              |                   |                               |              | 5                   | pS RMS | RMS                                                                                                                             |

| Cycle to Cycle Jitter                                      |                   |                               |              | 5                   | pS     |                                                                                                                                 |

|                                                            |                   |                               | SSB Ph       | ase Noise           |        |                                                                                                                                 |

|                                                            |                   |                               | -70          |                     | dBc/Hz | @ 10Hz Offset                                                                                                                   |

| Typical (100MHz)                                           |                   |                               | -104         |                     | dBc/Hz | @ 100Hz Offset                                                                                                                  |

| Typical (100MHz) Under Static Conditions                   |                   |                               | -123         |                     | dBc/Hz | @ 1000Hz Offset                                                                                                                 |

| Older Static Conditions                                    |                   |                               | -130         |                     | dBc/Hz | @ 10kHz Offset                                                                                                                  |

|                                                            |                   |                               | -135         |                     | dBc/Hz | @ 100kHz Offset                                                                                                                 |

|                                                            |                   |                               | Additional S | Specifications      |        |                                                                                                                                 |

| Tristate Enable Logic                                      |                   | 80% V <sub>DD</sub> or<br>N/C |              |                     | V      | Pad 1, Clock Signal Output                                                                                                      |

| Tristate Disable Logic                                     |                   |                               |              | 0.5                 | V      | Pad 1, Output to High-Z                                                                                                         |

| Start-up Time                                              | $T_{SU}$          |                               |              | 10                  | mS     |                                                                                                                                 |

|                                                            |                   |                               | Su           | pply                |        |                                                                                                                                 |

| Operating Voltage                                          | $V_{\mathrm{DD}}$ | 3.135                         | 3.3          | 3.465               | V      |                                                                                                                                 |

| Operating Current                                          | $I_{\mathrm{DD}}$ |                               | •            | 90                  | mΑ     |                                                                                                                                 |

|                                                            |                   |                               | Tempera      | ture Range          |        |                                                                                                                                 |

| Operating Temperature                                      | TA                | -55                           |              | +125                | °C     |                                                                                                                                 |

| Storage Temperature                                        | TS                | -55                           |              | +125                | °C     |                                                                                                                                 |

**Environmental, Mechanical & Test Report Requirements:**

| Mechanical Shock | Per MIL-STD-202, Method 213, Condition C (100 g's, 6 ms duration, ½ sinewave)         |

|------------------|---------------------------------------------------------------------------------------|

| Vibration        | Per MIL-STD-202, Method 201 & 204 (10 g's from 10-2000 Hz)                            |

| Thermal Cycle    | Per MIL-STD-883, Method 1010, B (-55°C to 125°C, 15 min. dwell, 10 cycles)            |

| Hermeticity      | Per MIL-STD-202, Method 112 (1 x 10 <sup>-8</sup> atm cc/s of Helium)                 |

| Solderability    | Per EIAJ-STD-002                                                                      |

| Package Type     | 6 Pad Ceramic Leadless or 4-lead Gull Wing Configuration (Ref. Figure 1 and Figure 2) |

## **Special Screening Steps:**

The parts shall be subjected to the following screening sequence after they are sealed.

- Burn-in: 168-hours minimum @ +125°C

- Frequency vs Temperature Test

- Final Electrical Test

# **MtronPTI HPO Series** For Harsh Environment Applications

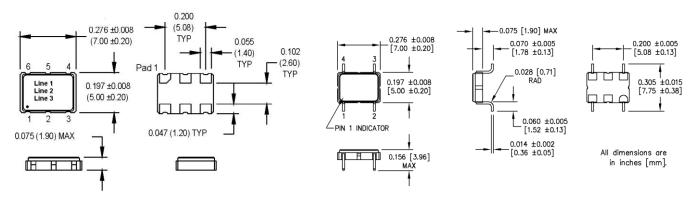

### Dimensions, Pin Out, & Marking Information:

| Pad | Lead | Function  |

|-----|------|-----------|

| 1   | 1    | Tristate  |

| 2   |      | N/C       |

| 3   | 2    | Ground    |

| 4   | 3    | Output    |

| 5   |      | N/C       |

| 6   | 4    | $+V_{DD}$ |

| Part Marking |            |  |

|--------------|------------|--|

| Line 1       | HPO-xxxx   |  |

| Line 2       | fffMffffff |  |

| Line 3       | M yyww     |  |

| Legend |           |  |  |

|--------|-----------|--|--|

| уу     | Year      |  |  |

| ww     | Work week |  |  |

|        |           |  |  |

Figure 1 - Leadless Configuration

Figure 2: Gull Wing Leaded Configuration

#### Part Number & Ordering Information:

| MtronPTI Model | Package Style     | Frequency Stability |

|----------------|-------------------|---------------------|

| HPO-310        | 6 mod Londloss    | ±50ppm              |

| HPO-311        | 6-pad Leadless    | ±25ppm              |

| HPO-320        | 4 Cull Wing Loads | ±50ppm              |

| HPO-321        | 4 Gull Wing Leads | ±25ppm              |

Order Code Convention: MtronPTI Model # and Frequency

(ex.; HPO-310-62.2080MHz: 6-pad leadless configuration, ±50ppm 20-year stability @ 62.208MHz)

Consult the factory for additional supply voltage requirements.

## **Datasheet Revision Table:**

| <br>     |      |        |                     |

|----------|------|--------|---------------------|

| Date     | Rev. | Author | Details of Revision |

| 05/23/13 | -    | BRM    | Original Release    |